1.067.335

kiadvánnyal nyújtjuk Magyarország legnagyobb antikvár könyv-kínálatát

VISSZA

A TETEJÉRE

JAVASLATOKÉszre-

vételek

RISC processzorok

Nyitott rendszerű képzés - távoktatás - oktatási segédlete/Tankönyv

| Kiadó: | LSI Oktatóközpont a Mikroelektronika Alkalmazásának Kultúrájáért Alapítvány |

|---|---|

| Kiadás helye: | Budapest |

| Kiadás éve: | |

| Kötés típusa: | Ragasztott papírkötés |

| Oldalszám: | 404 oldal |

| Sorozatcím: | |

| Kötetszám: | |

| Nyelv: | Magyar |

| Méret: | 24 cm x 17 cm |

| ISBN: | 963-577-155-x |

| Megjegyzés: | Fekete-fehér ábrákkal. |

naponta értesítjük a beérkező friss

kiadványokról

naponta értesítjük a beérkező friss

kiadványokról

Tartalom

| Tartalomjegyzék | 3 |

| Ábrák jegyzéke | 10 |

| Táblázatok jegyzéke | 14 |

| Előszó | 17 |

| Bevezetés | 21 |

| A szükséges alapismeretek | 21 |

| Alapfogalmak | 21 |

| Számítógépismeretek | 23 |

| A számítógépek általános felépítése, részei | 24 |

| Központi egység (processzor) | 25 |

| Tárolókezelés, memória | 28 |

| A RISC processzorok legfontosabb jellemzői | 30 |

| Processzorok teljesítőképessége | 33 |

| Teljesítőképesség mérése, összetevői | 33 |

| Utasításvégrehajtásonkénti ciklusok száma (C) | 35 |

| Ciklusok időtartama (T) | 39 |

| Utasítások száma (I) | 41 |

| Teljesítőképesség összesített mérése | 44 |

| Trendek | 46 |

| Teljesítőképesség tartalékai | 49 |

| Szuper-pipeline architektúra | 49 |

| Szuperskalár architektúra | 50 |

| RISC alapok | 51 |

| Előzmények, jellemzők | 52 |

| Előzmények | 52 |

| Jellemzők | 54 |

| Utasításkészlet | 58 |

| Utasításkészlet általános jellemzése | 58 |

| Utasításkészlet kialakításának statisztikai alapjai | 60 |

| Utasításszerkezet, címzési módok | 66 |

| Utasítástípusok | 70 |

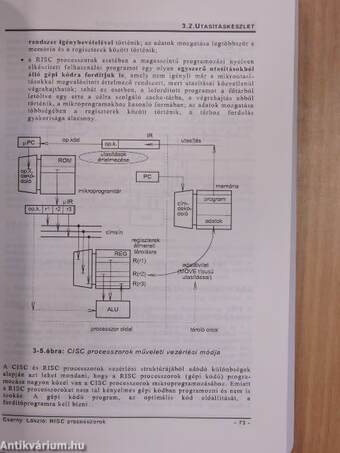

| Műveleti vezérlés | 72 |

| Utasításkészlet értékelése | 74 |

| Folyamatok párhuzamosítása (PIPELINING) | 75 |

| A párhuzamosítás lényege | 75 |

| Az utasításvégrehajtás gyorsítása | 77 |

| Műveletvégrehajtás gyorsítása | 101 |

| Pipeline-feldolgozás ütemezése | 103 |

| Továbblépés lehetőségei | 106 |

| Tárolókezelés | 106 |

| Tárolási alapfogalmak, tárolóhierarchia | 107 |

| Regisztertárak | 110 |

| Cache-tárak | 114 |

| Virtuális tárolókezelés | 129 |

| Fordítóprogram | 144 |

| Általános jellemzők | 144 |

| RISC fordítók jellegzetességei | 145 |

| Optimalizálás | 146 |

| Regiszterhasználat optimalizálása | 147 |

| Adatütközések feloldása | 151 |

| Megszakítások és kivételek | 151 |

| Megszakítás és kivétel fogalma, keletkezése | 151 |

| Megszakítások kiszolgálása, sorolása | 153 |

| ANSI/IEEE 754-es lebegőpontos adatkezelési szabvány | 155 |

| MIPS processzorok | 163 |

| Processzorok általános jellemzői | 163 |

| Felépítésük | 166 |

| Alapprocesszor (CPU) | 166 |

| Rendszervezérlő koprocesszor (CP0) | 167 |

| Lebegőpontos koprocesszor (CP1, FPU) | 167 |

| Utasításkészlet | 170 |

| Utasításfeldolgozás (PIPELINE) | 174 |

| Az utasításfeldolgozás lépései | 174 |

| A feldolgozás egyenletessé tétele | 176 |

| Tárolókezelés | 178 |

| Tárhierarchia | 178 |

| Virtuális memória | 179 |

| Cache-tárak | 191 |

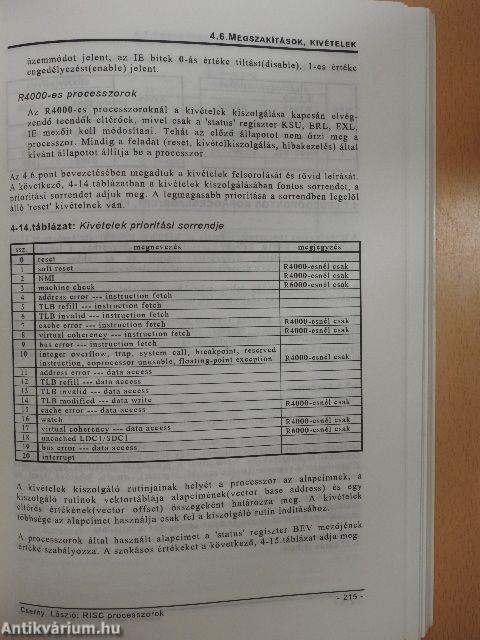

| Megszakítások, kivételek | 198 |

| A kivételkezelésben szerepet játszó regiszterek | 200 |

| Kivételek feldolgozása | 214 |

| Lebegőpontos koprocesszor (CP1, FPU) | 216 |

| Felépítés | 216 |

| Regiszterek és azok funkciója | 218 |

| Lebegőpontos utasítások, műveletek | 221 |

| Utasításfeldolgozás(PIPELINE) | 223 |

| Kivételek | 228 |

| PowerePc processzorok | 231 |

| PowerPc architektúra | 232 |

| Instruction Set Architecture | 233 |

| Virtual Environment Architecture | 234 |

| Operating Environment Architecture | 234 |

| Előzmények | 240 |

| Power RS1 | 240 |

| Power RS 9 | 242 |

| Power RSC | 243 |

| PowerPc 601 processzor | 244 |

| A processzor állapotai | 245 |

| Felépítése, részei | 246 |

| A processzor regiszterei | 251 |

| Adatelrendezés | 271 |

| Utasításkészlet | 272 |

| Utasításlista | 281 |

| Utasításfeldolgozás (pipeling) | 286 |

| Tárolókezelés | 290 |

| Kivételek | 305 |

| Kivételek listája | 308 |

| PowerPC 603, 604 processzorok | 310 |

| PowerPC 603 jellemzői | 310 |

| PowerPC 603 felépítése | 311 |

| PowerPC 603 utasításfeldolgozása | 315 |

| PowerPC 603 teljesítménye | 316 |

| PowerPC 604 processzor | 317 |

| Sparc processzorok | 319 |

| Általános jellemzők | 319 |

| Felépítés | 320 |

| Integer unit (IU) és regiszterei | 321 |

| Floating-point unit(FPU) és regiszterei | 332 |

| Utasítások, adatok | 338 |

| Adatformátumok | 338 |

| Utasításszerkezet, címzési módok | 343 |

| Utasítástípusok | 350 |

| Utasítások listája | 356 |

| Megszakítások, trap-ek | 359 |

| Trap lényege, jellemzői | 359 |

| Trap feldolgozása | 364 |

| Traplista | 367 |

| Tárolókezelés | 372 |

| Regisztertár | 372 |

| Tárolómodell | 374 |

| Virtuális címzés, MMU | 378 |

| A SPARC-V8 és V9 modellek közötti különbségek | 379 |

| Implementációk | 381 |

| UltraSPARC processzor | 381 |

| hyperSPARC processzor | 386 |

| superSPARC-II processzor | 388 |

| microSPARC-II processzor | 390 |

| Felhasznált irodalom | 393 |

| Tárgymutató | 395 |

Cserny László

Cserny László műveinek az Antikvarium.hu-n kapható vagy előjegyezhető listáját itt tekintheti meg: Cserny László könyvek, művekMegvásárolható példányok

Nincs megvásárolható példány

A könyv összes megrendelhető példánya elfogyott. Ha kívánja, előjegyezheti a könyvet, és amint a könyv egy újabb példánya elérhető lesz, értesítjük.